VGA Simulator: Getting Started

- xilinx

- isim

- simulation

- vhdl

- vga

- monitor

Go straight to the VGA Simulator

About

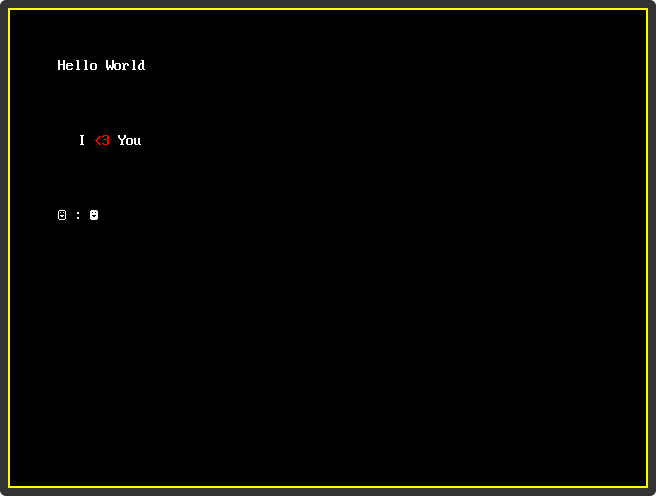

The VGA Simulator is a web based tool to easily view a raw VGA signal without having to hook it up to an actual CRT monitor. Easily review and save any frames generated. It uses horizontal sync, vertical sync, and red, green, blue to recreate pixel perfect frames.

The purpose of this tool was to create a faster way to debug FPGA/VHDL projects that utilize VGA. The problem is that synthesizing and generating a bit-file takes too long with Xilinx mainly because it only utilizes a single core. Although we have Simulators such as Isim to debug almost every aspect of a design, it is hard visualize a bunch a 1 or 0 flying past the screen on the rgb lines.

This tool is not VHDL specific, you just need to generate a log file with lines formatted as so: current_sim_time time_units: hs vs red green blue (ex. 535 ns: 1 1 010 010 01)

Workflow

- Create a test bench for your design.

- Add some code that logs the vga signal to a file.

- Run that log file in the VGA Simulator

Set up

- Create a test bench or open up an existing test bench

- Add the use statements for both the ieee and std to the top of your file with the rest of the using statements

use ieee.std_logic_textio.all; use std.textio.all; - Add the following process that logs to the file. The

clkneeds to be synchonized to your pixel clock and be just as fast or oversample your pixel clock. You can write your own logging, it just needs be formatted as so:current_sim_time time_units: hs vs red green blue(ex.535 ns: 1 1 010 010 01). Also seeLog File Formattingbelow.process (clk) file file_pointer: text is out "write.txt"; variable line_el: line; begin if rising_edge(clk) then -- Write the time write(line_el, now); -- write the line. write(line_el, ":"); -- write the line. -- Write the hsync write(line_el, " "); write(line_el, hsync); -- write the line. -- Write the vsync write(line_el, " "); write(line_el, vsync); -- write the line. -- Write the red write(line_el, " "); write(line_el, Red); -- write the line. -- Write the green write(line_el, " "); write(line_el, Green); -- write the line. -- Write the blue write(line_el, " "); write(line_el, Blue); -- write the line. -- write the contents into the file. writeline(file_pointer, line_el); end if; end process; - Run the test bench in

Isimor any other simulator - Find your log file and browse for it in the VGA Simulator tool. The log file should be in the same folder as the test bench or in the executable folder of your simulation tool.

- Optional: Set the

back porchin the fine tuning section. This will center your image in the canvas so that no clipping occurs. The back porch is the amount of pixel clock cycles after the rising edge of the sync pulses (hsync for back porch x, and vsync for back porch y). See this diagram (source) - Click submit and watch the frames generate

- You can also review any frames generated by the process by clicking the thumbnails.

- To save a frame, just make the frame the main monitor window and then click the

Download current framelink just above the monitor.

Log File Formatting / Syntax

- Must be a

.txtfile - Text file lines must be formatted as so

current_sim_time time_units: hs vs red green blue(ex.535 ns: 1 1 010 010 01) - Everything should be binary except sim time

- Pad red, green, and blue with

0(zeroes) to the max color depth - Log a line every rising edge of a clock that is synchronized with your pixel clock and is just as fast or oversamples.

- Make sure you set your clock period correctly in your testbench!